金属-氧化物-半导体集成电路(卷名:电子学与计算机)

metal-oxide-semiconductor integrated circuit

以金属-氧化物-半导体(MOS)器件为基础的单片集成电路。主要是以硅为衬底,SiO2为氧化层的硅 MOS集成电路。实际上,还有以蓝宝石为衬底,其上外延生长硅单晶层制作的 MOS集成电路和以砷化镓等高迁移率材料为衬底的砷化镓MOS集成电路等。

发展简况 1959年,利用场效应原理研制成MOS场效应晶体管。后又把MOS技术用于MOS集成电路的研究,并于 1962年研制成功。MOS集成电路比双极型集成电路更便于实现大规模集成,所以很快地向中规模和大规模集成方向发展。1968年,出现了大规模集成电路的 P沟道MOS存储器。随后,单片MOS计算器、MOS微处理器也相继于1970年和1971年间问世。

60年代,MOS集成电路主要是铝栅P沟道电路。这种MOS集成电路的电源电压较高(18~20伏),常需要两个电源,而且与外部电路连接要有专门的接口电路,使用不很方便。此外,在铝栅MOS工艺中,必须先做源、漏PN结,最后才能制作铝栅(因铝层不能经受高温处理)。因而,版图设计中,栅源和栅漏需有相当的覆盖,覆盖电容较大。P沟道导电载流子空穴的迁移率比电子低,所以,铝栅P沟道MOS集成电路的速度较低,一般只能用到1~2兆赫。70年代前期研制成功硅栅N沟道MOS(NMOS)电路(见N沟道金属-氧化物-半导体集成电路),很快便取代了铝栅PMOS电路。NMOS电路的出现比 PMOS电路(见P沟道金属-氧化物-半导体集成电路)迟了将近10年,主要原因是NMOS电路要求更纯净的SiO2膜、更少的可动电荷和固定电荷、更低的界面态密度。

硅 MOS集成电路的集成度(以动态随机存储器为代表)到1975年前后,几乎以每 2年提高 4倍的速度增长。这是下面三方面技术进展的结果:①在硅片质量不断提高的基础上,芯片面积不断增大;②电路设计的创新使单元电路面积不断缩小;③光刻精度不断提高保证了集成电路元件集成密度的持续提高。70年代后期以来,由于电路革新比较迟缓,集成度增长上升速度稍缓,但仍为每3年左右提高4倍。

70年代末期之前,MOS集成电路只是在数字电路领域发挥较大的作用;在模拟量处理方面双极型集成电路处于优势。但是进入80年代以后,由于 MOS大规模集成电路性能价格比不断提高,MOS数-模和模-数转换器的发展也很快。在 MOS芯片上对模拟量进行离散化处理的技术有很大的发展,已研制出一些MOS模拟集成电路,如运算放大器和开关电容滤波器等。在此基础上,各种通用和专用的信号处理器产品日益增多,MOS大规模集成电路已广泛用于通信,特别是电话通信、图像和语音识别等新的领域。

电路形式和基本结构 图1为基本MOS反相器的电路形式。图2是与图1a对应的增强型 MOS场效应晶体管负载反相器的剖面图和俯示版图。反相器由T1和T2两个MOS场效应晶体管组成。T1用作负载,称为负载管,T2称为工作管。通常,后级工作管的栅电容连同PN结寄生电容,就是前级的负载。当T2的输入端电压(Ui)小于其阈电压(

)即Ui<

)即Ui< -δ1(δ为必要的余量)时,T2截止,电源通过T1向负载电容充电,使输出电压U0达到高电平(UDD-

-δ1(δ为必要的余量)时,T2截止,电源通过T1向负载电容充电,使输出电压U0达到高电平(UDD- )(UDD为电源电压)。这一高电平应比工作管的阈电压

)(UDD为电源电压)。这一高电平应比工作管的阈电压 大δ2以上,即U0=UDD-

大δ2以上,即U0=UDD- >

> +δ2。 当T2输入电平为高电平(Ui>

+δ2。 当T2输入电平为高电平(Ui> +δ2)时,T2导通,使负载电容对地放电,U0降低,其最后数值决定于T2与T1的导通电阻之比。除工作电压因素外,T2、T1导通电阻之比取决于导电因子β之比。而β正比于 MOS场效应管的宽长比(W/L)、栅电容C

+δ2)时,T2导通,使负载电容对地放电,U0降低,其最后数值决定于T2与T1的导通电阻之比。除工作电压因素外,T2、T1导通电阻之比取决于导电因子β之比。而β正比于 MOS场效应管的宽长比(W/L)、栅电容C 和迁移率μ,β=μC

和迁移率μ,β=μC (W/L)。因此,适当选择(W/L)1和(W/L)2的比例,就可以在Ui为高电平时使U0为低电平(U0<

(W/L)。因此,适当选择(W/L)1和(W/L)2的比例,就可以在Ui为高电平时使U0为低电平(U0< -δ1),从而实现信号的反相和放大。这种反相器与 MOS场效应晶体管开关相结合,便能组成各种MOS数字集成电路。

-δ1),从而实现信号的反相和放大。这种反相器与 MOS场效应晶体管开关相结合,便能组成各种MOS数字集成电路。

依反相器负载器件的不同,MOS电路可分为图1中的几种形式。图1 a是以增强型MOS场效应晶体管为负载管的增强型-增强型电路;图1b的负载管是耗尽型MOS场效应晶体管,通过沟道区离子注入掺杂使UT<0而形成的。这种电路称为增强型与耗尽型金属-氧化物-半导体集成电路;图1c以电阻为负载,称为增强型-电阻电路;图1d的反相器由两只导电类型相反的即PMOS和NMOS场效应晶体管所组成,推挽工作,称为CMOS电路。增强型-增强型电路的优点是工艺简单,但工作速度和功率消耗的综合指标即功耗与延时乘积最差,逻辑摆幅也低(最高电平为UDD-

)。增强型-耗尽型(D-MOS)电路的D负载管,在零栅压下仍然导通,因而逻辑摆幅大(最高电平为UDD)。按图1b连接时,D-MOS场效应晶体管对负载的充电接近恒流,因而充电速度快,电路可以达到很高的工作速度,有较低的功耗与延时乘积。此外,经适当设计,增强型-耗尽型反相器的宽长比(W/L)常可取为1/1左右,对缩小版图面积有利。增强型-耗尽型电路的问题是工艺较复杂,在超大规模集成电路中,其直流功耗嫌太大。增强型-电阻电路的速度也较快,逻辑摆幅也大。利用离子注入到SiO2层上的多晶硅条,已能制作各种阻值的电阻,只占用很小的硅片面积。因此,这种电路形式已在不少场合得到有效应用。CMOS反相器中的两只 MOS场效应晶体管随不同的输入电平总是一只导通,另一只截止,没有直流导通电流(只是在状态变化的瞬间有电流导通)。因此,CMOS电路是功耗最低的电路。为了将两种导电类型不同的MOS场效应晶体管做在一个芯片上,CMOS须为其中一种管子制作专门的隔离阱(利用扩散或离子注入进行掺杂)。一般说,CMOS电路工艺比较复杂,面积也比较大。在面积太小时,还会出现所谓的闸锁效应(见互补金属-氧化物-半导体集成电路)。在超大规模集成电路的发展中,降低功耗密度是首要问题,所以CMOS在超大规模集成电路中是一种主要的技术。实际上,由于工艺技术的不断发展,人们正在研究将上述几种电路形式(包括双极电路)协调兼容在一个芯片上的技术,这使大规模集成电路的设计有更大的灵活性和更高的性能价格比。

)。增强型-耗尽型(D-MOS)电路的D负载管,在零栅压下仍然导通,因而逻辑摆幅大(最高电平为UDD)。按图1b连接时,D-MOS场效应晶体管对负载的充电接近恒流,因而充电速度快,电路可以达到很高的工作速度,有较低的功耗与延时乘积。此外,经适当设计,增强型-耗尽型反相器的宽长比(W/L)常可取为1/1左右,对缩小版图面积有利。增强型-耗尽型电路的问题是工艺较复杂,在超大规模集成电路中,其直流功耗嫌太大。增强型-电阻电路的速度也较快,逻辑摆幅也大。利用离子注入到SiO2层上的多晶硅条,已能制作各种阻值的电阻,只占用很小的硅片面积。因此,这种电路形式已在不少场合得到有效应用。CMOS反相器中的两只 MOS场效应晶体管随不同的输入电平总是一只导通,另一只截止,没有直流导通电流(只是在状态变化的瞬间有电流导通)。因此,CMOS电路是功耗最低的电路。为了将两种导电类型不同的MOS场效应晶体管做在一个芯片上,CMOS须为其中一种管子制作专门的隔离阱(利用扩散或离子注入进行掺杂)。一般说,CMOS电路工艺比较复杂,面积也比较大。在面积太小时,还会出现所谓的闸锁效应(见互补金属-氧化物-半导体集成电路)。在超大规模集成电路的发展中,降低功耗密度是首要问题,所以CMOS在超大规模集成电路中是一种主要的技术。实际上,由于工艺技术的不断发展,人们正在研究将上述几种电路形式(包括双极电路)协调兼容在一个芯片上的技术,这使大规模集成电路的设计有更大的灵活性和更高的性能价格比。在静态工作条件下,为了保证输出有良好的低电平,T1和T2的宽长应有一定的比值(CMOS除外)。因此,这种MOS电路被称为有比电路。如果负载管的栅电压或漏电压用时钟脉冲馈电,利用负载电容的电荷存储性质,此馈电脉冲可与输入脉冲Ui在不同的时间交错馈入。这时的MOS电路便处于动态工作状态,称为动态MOS电路。动态MOS电路的电流通导时间短,一般没有T1和T2之间宽长比的要求,称为无比电路。MOS动态电路具有面积小、功耗低等优点,而且可利用各种自举形式提高输出电平,可大大加快电路的工作速度。因此,在MOS大规模集成电路设计中,动态设计十分重要。如果与静态电路相结合,可大大提高MOS大规模集成电路的性能。

从结构或工艺技术来说,MOS集成电路大体上可以分为PMOS、NMOS、和CMOS三类。各类中又有铝栅、硅栅等的区别。超大规模集成电路技术已开始采用高熔点金属或其硅化物制作栅,但实质上仍可把他们归到硅栅技术一类。由于硅栅NMOS在速度、面积各方面都远优于铝栅PMOS结构,除少数小型或廉价的MOS集成电路以外,已很少采用PMOS和铝栅技术。对硅栅(或高熔点金属及其硅化物栅)NMOS,依照尺寸按比例缩小的原则,随着器件尺寸的适当缩小,每级门的延时与功耗乘积会大大降低,即性能可以大大提高。作为尺寸缩小的直接后果,集成度也会相应提高。向这个方向发展的 MOS集成电路技术以及相应的结构,称为HMOS(见高性能金属-氧化物-半导体集成电路。CMOS技术可以分为P阱和N阱两种(图3a,b)。这两种 CMOS结构各有长处。过去,由于CMOS产品是从PMOS发展而来的,故P阱居多。但N阱CMOS发展很快。

除了上述几种常用的MOS集成电路结构外,还有一些特殊的MOS集成电路结构形式。其中,比较成功的有:①DMOS(见双扩散金属-氧化物-半导体集成电路)或 DSA MOS(扩散自对准MOS结构,图4a)。它利用侧向扩散效应,使自对准的沟道长达微米和亚微米水平,从而获得很高的电路工作速度;②VMOS或UMOS,即V型槽或U型槽MOS结构(见V型槽金属-氧化物-半导体集成电路)。它是利用特定晶向Si晶体的择优腐蚀特性,把MOS场效应管做在V型或U型槽内,而利用扩散、离子注入或外延方法控制其沟道长度(图4b),使其达到亚微米水平,以实现高速度。V型或U型槽对缩小芯片面积也有一定的意义;③以蓝宝石为衬底的CMOS结构称为SOS CMOS。在绝缘衬底上制作CMOS电路,不需要制作专门的隔离阱,PN结面积和寄生电容也很小。因此,这种结构不仅功耗低,而且速度快,抗辐照性能很好。这种集成电路技术在军事上具有重要的意义。

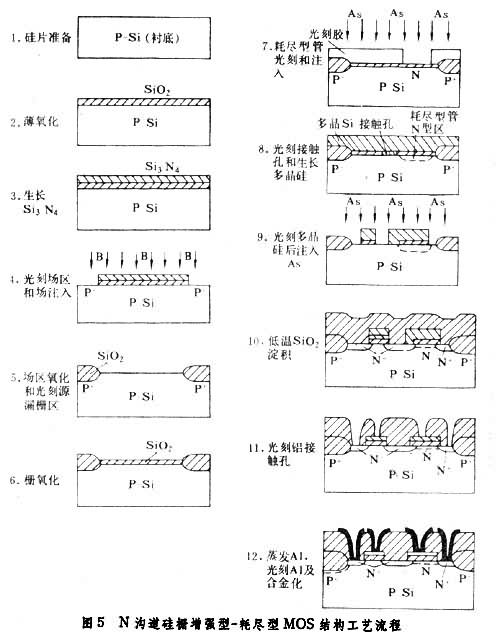

工艺和特点 以硅栅NMOS为例,MOS集成电路的有源元件是MOS场效应管,无源元件是MOS电容和PN结电容,有时还有多晶硅电阻。元件间的隔离利用厚氧化层(称为场氧化层);元件间的互连线同时使用扩散(或注入)层、多晶硅层和最后的金属化层。它结构简单,元件的工艺又都是兼容的,工艺也不复杂。图5是 NMOS电路主要工艺流程示意图。在切割、研磨和抛光完毕的P型(100)硅衬底上,用等平面工艺(衬底薄氧化后生长Si3N4掩蔽层,光刻出场氧区,进行B+硼场注入,然后在场区生长厚度约1微米左右的场氧化层)生长场氧化层,把非场区,即制作元件的区间刻蚀出来,进行MOS场效应管和MOS电容的栅氧化(此前,如需要进行栅区注入,应增加相应的光刻和注入工艺);刻出多晶硅与扩散区相接的接触孔(埋孔);进行掺杂(一般掺磷),多晶硅化学汽相淀积(CVD);如需要多晶硅电阻,则要利用光刻掩蔽对多晶硅电阻区单独进行特定剂量的离子注入(用磷和砷);光刻多晶硅,刻出栅和多晶硅连线,并暴露出需要掺杂或注入的区域(包括源、漏衬底内的连线区);进行扩散和离子注入(必要时,加入光刻限定扩散和注入区);短时间低温热氧化后,用化学汽相淀积工艺淀积磷硅玻璃,光刻出铝层与多晶硅、扩散区、注入区的接触孔;短时间加温,使磷硅玻璃体稍有流动,以钝化台阶陡度,后蒸发铝层,再合金化、光刻铝布线和压焊块,最后进行中间测试、压焊、封装、成品测试。对于复杂的 MOS大规模集成电路中间还有一些工艺步骤,一般需要经过8、9道乃至10道以上的光刻步骤。MOS大规模集成电路工艺,实质上就是一般的硅平面工艺,只是增加了以下一些工艺步骤:①多晶硅技术;②等平面场氧化技术,提高连线的可靠性,保证有效的场隔离;③利用定剂量的离子注入技术调整MOS场效应管的阈电压。

与双极型集成电路相比,MOS集成电路的特点是:①结构简单,隔离方便(除CMOS外,有PN结自动隔离,只须用较厚的下面注有浓硼的场氧化层即可实现有效隔离);② MOS场效应管为双向器件(源、漏结构对称)又有多晶硅作为一层布线层。布线方便,设计灵活性高,版图占面积小;③MOS电路的功耗低于双极型电路,与双极型集成电路相比,更适宜于高密度集成;④MOS集成电路具有动态工作独特的能力;⑤MOS场效应管是多子器件,其温度特性优于双极型集成电路。但是,硅MOS集成电路的速度还比不上ECL等高速双极集成电路。一般认为,MOS集成电路的功耗低,集成度高,宜于数字应用;双极型集成电路则适用于高速数字和模拟方面。

发展方向 MOS集成电路的主要发展方向有:①进一步提高集成密度和电路复杂性,即由集成电路向集成系统发展。②超高速化和微功耗化。军事应用已对超高速集成电路提出迫切的要求,许多国家大力发展超高速集成电路,主要是砷化镓大规模集成电路。由于在砷化镓、磷化铟等半导体中业已发现,当沟道缩短到亚微米以下时,会出现饱和速度过冲及冲击式的电输运现象,并利用分子束外延制成高电子迁移率晶体管等高速集成器件,为 MOS集成电路的超高速化开辟了新的前景。③研究三维集成技术和研制以新型器件为基础的集成电路。集成系统日趋复杂,连线所占的芯片面积越来越大,连线的设计也越来越困难和费时,所以具有多层元件布局的MOS大规模集成结构受到很大重视。

参考书目

清华大学微电子学研究所编:《MOS大规模集成技术》,科学出版社,北京,1984。